#### **COMPITO A**

#### Esercizio 1 (17 punti)

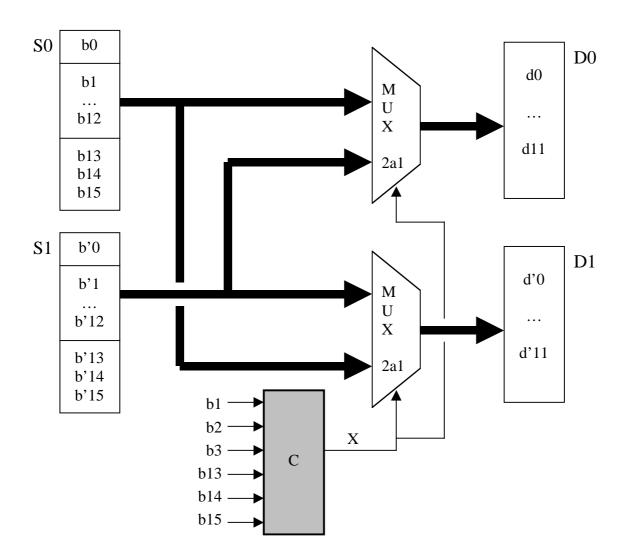

Si hanno a disposizione due registri sorgente S0 e S1 da 16 bit che contengono reali memorizzati in rappresentazione a virgola mobile normalizzata : il primo bit  $(b_0)$  rappresenta il segno, i successivi 12 bit  $8(b_1,b_2...b_{12})$  rappresentano la mantissa (normalizzata) e gli ultimi 3 bit  $(b_{13}b_{14}b_{15})$  l'esponente in complemento a due. Si dispone anche di due registri destinazione da 12 bit D0 e D1. Si vuole realizzare la seguente interconnessione:

- se la parte intera del numero reale memorizzato in S0 è pari, allora trasferisci la mantissa del numero contenuto in Si nel registro Di (S0→D0, S1→D1)

- altrimenti S0 $\rightarrow$ D1, S1 $\rightarrow$ D0

(<u>NotaBene</u>: non richiesto che la mantissa del numero in S0 sia pari, ma che lo sia la <u>parte</u> intera del numero in virgola fissa corrispondente. Pertanto necessario riflettere su come sono collegati la rappresentazione in virgola mobile normalizzata di un numero reale e il numero reale effettivamente codificato in questo modo. Dovete passare, per ogni valore della tripla  $b_{13}b_{14}b_{15}$ , dalla rappresentazione in virgola mobile a quella in virgola fissa, e osservare quale sia l'ultimo bit della parte intera del numero così ottenuto).

Si descriva in dettaglio il circuito di interconnessione.

OSSERVAZIONE (che non dovrebbe <u>proprio</u> essere necessaria): dovete progettare un circuito COMBINATORIO!!!

#### Esercizio 2 (13 punti).

Si progetti un comparatore aritmetico SEQUENZIALE. Il comparatore riceve due stringhe di ingresso X(n)=x0x1...xn ..... Y(n)=y0y1...yn (xi,yi rappresentano la coppia di bit ricevuta nell'istante ti), e produce in ogni istante ti un'uscita zi=1 sse la stringa X(i)>Y(i) (quindi verifica una maggioranza stretta).

## **Compito B**

## Esercizio 1 (17 punti)

Si progetti il circuito di controllo di un semaforo. Il funzionamento richiesto è il seguente:

- il semaforo deve tenere accesa per 10 secondi la luce verde

- poi deve spegnere la luce verde e tenere accesa per 6 secondi la luce gialla

- poi deve spegnere la luce gialla e tenere accesa per 16 secondi la luce rossa

- infine deve spegnere la luce rossa e ricominciare

Si assuma di avere a disposizione un clock con una frequenza di 1 Herz (cioè un impulso ogni secondo). Si utilizzino FF di tipo JK e non si dia per scontato l'utilizzo di alcun modulo predefinito (cioè, se si usa un qualche modulo visto a lezione è necessario mostrarne in dettaglio l'architettura, fino a porte logiche e FF). Per i contatori, potete usare un modulo predefinito, visto che sono oggetto del successivo esercizio.

### Esercizio 2 (10 punti)

Progettate nel dettaglio un contatore sincrono parallelo modulo 32 con FF di tipo JK.

## Esercizio 3 (2 punti)

Quale è la codifica in decimale delle stringhe 1000 e 0001 in complemento a due?

## **Compito C**

## Esercizio 1 (14 punti).

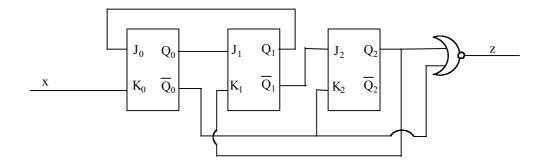

Analizzare il seguente circuito sequenziale e ricavare il diagramma di stato.

## Esercizio 2 (14 punti).

Progettare un circuito il cui output è 1 quando viene riconosciuta una delle seguenti stringhe: 001, 101 oppure 000. L'output è zero altrimenti.

Il primo bit che viene letto è il bit **più a sinistra**. Le stringhe sono *sovrapponibili*, nel senso chiarito a lezione.

Pur non essendo richiesta l'applicazione di un criterio formale di minimizzazione dell'automa, sarà elemento di valutazione il numero degli stati complessivi utilizzati.

### Esercizio 3 (2 punti)

Dati tre bit b2b1b0 scrivere tutte le possibili configurazioni di questi tre bit in complemento a due, con accanto il rispettivo numero intero con segno.

## **Compito D**

## Esercizio 1 (14 punti).

Analizzare il seguente circuito sequenziale e ricavare il diagramma di stato:

## Esercizio 2 (14 punti).

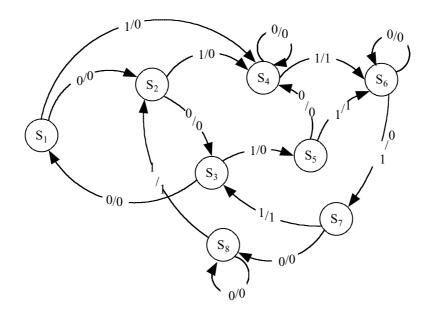

Minimizzare il seguente automa e progettare il relativo circuito utilizzando FF di tipo JK:

## Esercizio 3 (2 punti)

In complemento a due, che valore hanno le stringhe 0011 e 1111 ?

## Soluzione compito A

#### Esercizio 1

Si hanno a disposizione due registri sorgente S0 e S1 da 16 bit che contengono reali memorizzati in rappresentazione a virgola mobile normalizzata : il primo bit  $(b_0)$  rappresenta il segno, i successivi 12 bit  $8(b_1,b_2...b_{12})$  rappresentano la mantissa (normalizzata) e gli ultimi 3 bit  $(b_{13}b_{14}b_{15})$  l'esponente in complemento a due. Si dispone anche di due registri destinazione da 12 bit D0 e D1. Si vuole realizzare la seguente interconnessione:

- se la parte intera del numero reale memorizzato in S0 è pari, allora trasferisci la mantissa del numero contenuto in Si nel registro Di (S0→D0, S1→D1)

- altrimenti S0 $\rightarrow$ D1, S1 $\rightarrow$ D0

Diciamo che i registri sorgente siano del tipo

| b0 b1 |  | b12 1 | b13 | ••• | b15 |

|-------|--|-------|-----|-----|-----|

|-------|--|-------|-----|-----|-----|

dove b0 il bit di segno, b1//b12 sono i bit della mantissa e b13/b14/b15 i bit dell esponente. Il numero in virgola fissa corrispondente dunque espresso come:

$$\pm 0, b_1b_2b_3...b_{12} \times 2^{b_{13}b_{14}b_{15}}$$

Ed inoltre in Ca2 si ha per l'esponente:

| b13b14b15 | decimale |

|-----------|----------|

| 011       | +3       |

| 010       | +2       |

| 001       | +1       |

| 000       | 0        |

| 111       | -1       |

| 110       | -2       |

| 101       | -3       |

| 111       | -4       |

Per definire il circuito di controllo, basta osservare che

- se b13 = 1 oppure b13 = b14 = b15 = 0 allora il numero ha parte intera uguale a 0 (che quindi è pari) Infatti, se l'esponente è zero o negativo, il numero decimale corrispondente avrà certamente la parte intera uguale a zero.

- se b13 b14 b15 = 001 allora il numero decimale corrispondente, a meno del segno, sarà: b1,b2b3..b12

la parte intera è dunque b1 (che quindi è pari sse b1 è 0)

- se b13 b14 b15 = 010 allora la parte intera è b1 b2 (che quindi è pari sse b2 è 0)

- se b13 b14 b15 = 011 allora la parte intera è b1 b2 b3 (che quindi è pari sse b3 è 0)

Volendo rappresentare tutto questo mediante una tabella di verità, avrò:

| b13b14b15 | bit  | (X)  | che    | determina | la | parit |  |

|-----------|------|------|--------|-----------|----|-------|--|

|           | (0=1 | rue, | 1=fals | se)       |    |       |  |

| 011 | se b3=0 true, altrimenti false |

|-----|--------------------------------|

| 010 | se b2=0 true, altrimenti false |

| 001 | se b1=0 true, altrimenti false |

| 000 | true                           |

| 111 | true                           |

| 110 | true                           |

| 101 | true                           |

| 111 | true                           |

Pertanto il primo trasferimento verrà effettuato se e solo se X=1, dove X è definito come  $X=b13+\underline{b}13\,\underline{b}14\,\underline{b}15+\underline{b}1\,\underline{b}13\,\underline{b}14\,\underline{b}15+\underline{b}2\,\underline{b}13\,\underline{b}14\,\underline{b}15+\underline{b}3\,\underline{b}13\,\underline{b}14\,\underline{b}15$  (la sootolineatura significa negazione) Infatti, X vale 1 se e solo se uno dei quttro casi sopra elencati si verifica. Sia C il circuito che prende in input b1/b2/b3/b13/b14/b15 e d in output 1 sse X=1. La rete di interconnessione richiesta pertanto

dove la linea spessa contiene solo i 12 bit delle mantisse. Inoltre i multiplexer selezionano l'input più in alto se il segnale di controllo vale 1, l'input più in basso altrimenti.

#### Esercizio 2.

Questo esercizio è del tutto analogo al progetto di un sommatore sequenziale che è stato fatto durante una esercitazione e fa anche parte delle prove circuitmaker 2003-2004.

L'automa può trovarsi in due stati possibili: S0, in cui il risultato della precedente comparazione ha prodotto z=0, ed S1, in cui il risultato della precedente comparazione ha prodotto z=1.

L'automa (descritto mediante tabella di transizione) è il seguente:

| Stato di partenza↓ /Input (xy)→ | 00   | 01   | 10   | 11   |

|---------------------------------|------|------|------|------|

| S0                              | 0/S0 | 0/S0 | 1/S1 | 0/S0 |

| S1                              | 1/S1 | 0/S0 | 1/S1 | 1/S1 |

Poichè l'output coincide con l'informazione che occorre tenere in memoria, conviene un automa di Moore.

### **Compito B**

#### Esercizi 1 e 2

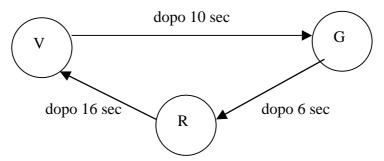

Intuitivamente, l'automa di Moore che descrive il comportamento richiesto è il seguente.

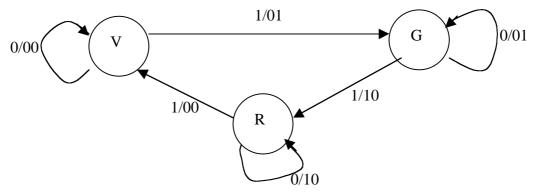

Se disponessimo di un circuito C che continuamente dia in output 1 una volta contati 10 segnali di clock, poi dia in output nuovamente 1 una volta contati altri 6 segnali di clock ed infine dia in output 1 una volta contati altri 16 segnali di clock (e in tutti i momenti intermedi dà in output 0), l'automa verrebbe tradotto nell'automa di Mealy (dove associamo alle uscite Z0Z1 = 00 l'accensione del verde e lo spegnimento delle altre due luci, a 01 l'accensione del giallo e lo spegnimento delle altre due luci, e a 10 l'accensione del rosso e lo spegnimento delle altre due luci).

Facciamo la sintesi di questo automa, lasciando per dopo la sintesi del circuito C. Associamo a V, G e R le ovvie codifiche Q0Q1 = 00, 01, 10. Da ciò la tabella degli stati futuri è

| X | Q0 | Q1 | Z0 | <b>Z</b> 1 | Q0 | Q1 (t+1) | J0 | K0 | J1 | K1 |

|---|----|----|----|------------|----|----------|----|----|----|----|

| 0 | 0  | 0  | 0  | 0          | 0  | 0        | 0  | -  | 0  | -  |

| 0 | 0  | 1  | 0  | 1          | 0  | 1        | 0  | -  | -  | 0  |

| 0 | 1  | 0  | 1  | 0          | 1  | 0        | -  | 0  | 0  | -  |

| 0 | 1  | 1  | -  | -          | -  | -        | -  | -  | -  | -  |

| 1 | 0  | 0  | 0  | 1          | 0  | 1        | 0  | -  | 1  | -  |

| 1 | 0  | 1  | 1  | 0          | 1  | 0        | 1  | -  | -  | 1  |

| 1 | 1  | 0  | 0  | 0          | 0  | 0        | -  | 1  | 0  | -  |

| 1 | 1  | 1  | -  | -          | -  | -        | -  | -  | -  | -  |

Usando le mappe di Karnaugh si ottengono le espressioni minime

$$Z0 = \underline{x} \ Q0 + x \ Q1$$

$Z1 = \underline{x} \ Q1 + x \ \underline{Q0} \ \underline{Q1}$   $J0 = x \ Q1$   $J1 = x \ \underline{Q0}$   $K0 = K1 = x$  da cui è immediato ricavare il circuito risultante D.

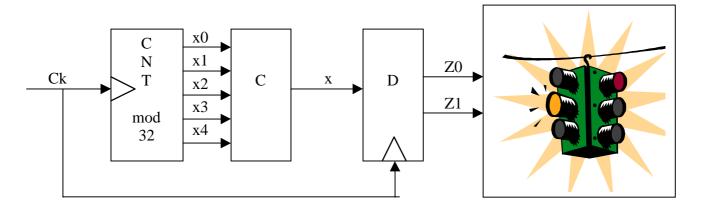

Supponiamo di avere un **contatore modulo 32** (l esrcizio 2 richiedeva di disegnarne esplicitamente lo schema circuitale) che prenda in input il clock con frequenza 1 Hz e diamo in input a C le cinque uscite x4/x3/x2/x1/x0 del contatore. Il circuito C dovr implementare la funzione booleana che d 1 se e solo se

In questa maniera, prendendo come stato iniziale R e il contatore resettato, abbiamo il compartamento desiderato. Ovviamente, l'output di C sarà l'input x del circuito D (sintetizzato a partire dall'automa appena mostrato). Pertanto, utilizzando il procedimento per ottenere la forma canonica disgiuntiva e usando poi gli assiomi dell'algebra di Boole, si ottiene che

$$x = \underbrace{x4 \ x3 \ x2 \ x1 \ x0}_{= \ x3 \ x2 \ x1 \ x0} + x4 \ x3 \ x2 \ x1 \ x0}_{= \ x2 \ x0} + \underbrace{x4 \ x3 \ x2 \ x1 \ x0}_{= \ x4 \ x3 \ x2}_{= \ x4 \ x3 \ x1}$$

che è la funzione che C deve calcolare. In definitiva, il circuito richiesto è ottenuto come segue

**OSS**: l'esercizio poteva essere risolto <u>più semplicemente</u> prendendo il contatore MOD 32 ed associare alle uscite da 00000 a 01010 la luce verde, da 01011 a 10000 la luce gialla e da 10001 a 11111 la luce rossa.

# Soluzione compito C

## Esercizio 1

Si ha:

$$\begin{split} J_0 &= Q_1 \\ K_0 &= x \\ J_1 &= Q_0 \\ K_1 &= Q_2 \\ J_2 &= \overline{Q_1} \\ K_2 &= \overline{Q_0} \\ z &= \overline{\overline{Q_0} + Q_2} = Q_0 \cdot \overline{Q_2} \end{split}$$

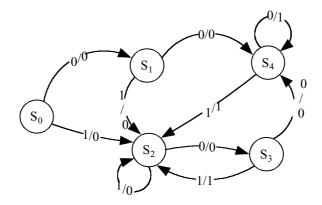

Il diagramma degli stati è il seguente:

| X | $Q_2(t)$ | $Q_1(t)$ | $Q_0(t)$ | $\mathbf{J}_2$ | $\mathbf{K}_{2}$ | $\mathbf{J}_1$ | $\mathbf{K}_{1}$ | $\mathbf{J_0}$ | $\mathbf{K}_{0}$ | $Q_2(t+1)$ | $Q_1(t+1)$ | $Q_0(t+1)$ | Z |

|---|----------|----------|----------|----------------|------------------|----------------|------------------|----------------|------------------|------------|------------|------------|---|

| 0 | 0        | 0        | 0        | 1              | 1                | 0              | 0                | 0              | 0                | 1          | 0          | 0          | 0 |

| 0 | 0        | 0        | 1        | 1              | 0                | 1              | 0                | 0              | 0                | 1          | 1          | 1          | 1 |

| 0 | 0        | 1        | 0        | 0              | 1                | 0              | 0                | 1              | 0                | 0          | 1          | 1          | 0 |

| 0 | 0        | 1        | 1        | 0              | 0                | 1              | 0                | 1              | 0                | 0          | 1          | 1          | 1 |

| 0 | 1        | 0        | 0        | 1              | 1                | 0              | 1                | 0              | 0                | 0          | 0          | 0          | 0 |

| 0 | 1        | 0        | 1        | 1              | 0                | 1              | 1                | 0              | 0                | 1          | 1          | 1          | 0 |

| 0 | 1        | 1        | 0        | 0              | 1                | 0              | 1                | 1              | 0                | 0          | 0          | 1          | 0 |

| 0 | 1        | 1        | 1        | 0              | 0                | 1              | 1                | 1              | 0                | 1          | 0          | 1          | 0 |

| 1 | 0        | 0        | 0        | 1              | 1                | 0              | 0                | 0              | 1                | 1          | 0          | 0          | 0 |

| 1 | 0        | 0        | 1        | 1              | 0                | 1              | 0                | 0              | 1                | 1          | 1          | 0          | 1 |

| 1 | 0        | 1        | 0        | 0              | 1                | 0              | 0                | 1              | 1                | 0          | 1          | 1          | 0 |

| 1 | 0        | 1        | 1        | 0              | 0                | 1              | 0                | 1              | 1                | 0          | 1          | 0          | 1 |

| 1 | 1        | 0        | 0        | 1              | 1                | 0              | 1                | 0              | 1                | 0          | 0          | 0          | 0 |

| 1 | 1        | 0        | 1        | 1              | 0                | 1              | 1                | 0              | 1                | 1          | 1          | 0          | 0 |

| 1 | 1        | 1        | 0        | 0              | 1                | 0              | 1                | 1              | 1                | 0          | 0          | 1          | 0 |

| 1 | 1        | 1        | 1        | 0              | 0                | 1              | 1                | 1              | 1                | 1          | 0          | 0          | 0 |

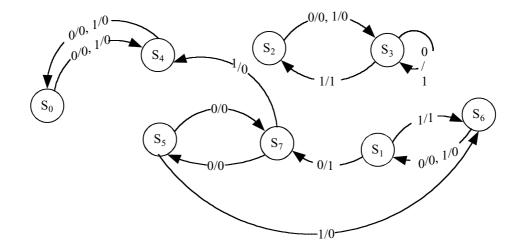

L'automa di Mealy relativo è il seguente:

L'automa è minimizzabile: gli stati  $S_0$  e  $S_4$  possono essere fusi in un unico stato.

#### Esercizio 2

L'automa di Mealy è il seguente:

dove:

- S<sub>0</sub> indica lo stato iniziale

- S<sub>1</sub> lo stato in cui è stato riconosciuto "0"

- S<sub>4</sub> lo stato in cui è stata riconosciuta una stringa "00...0" di lunghezza almeno 2

- S<sub>2</sub> lo stato in cui è stato riconosciuto un "1"

- S<sub>3</sub> lo stato in cui è stato riconosciuto "10"

Si noti che non è necessario tenere uno stato per la stringa "101" perché è sufficiente tenere traccia dell'ultimo "1". Infatti concatenando un bit alla stringa "101" non si ottiene nessuna sequenza valida. Lo stesso ragionamento si può applicare alla stringa "001" e così via.

Si poteva anche realizzare l'automa con tutti i possibili stati e poi minimizzarlo, ma sarebbe stato più laborioso.

| Stato | Input 0           | Input 1   |

|-------|-------------------|-----------|

| $S_0$ | $S_{1}/0$         | $S_{2}/0$ |

| $S_1$ | S <sub>4</sub> /0 | $S_{2}/0$ |

| $S_2$ | S <sub>3</sub> /0 | $S_{2}/0$ |

| $S_3$ | S <sub>4</sub> /0 | $S_{2}/1$ |

|-------|-------------------|-----------|

| $S_4$ | S <sub>4</sub> /1 | $S_2/1$   |

Gli stati si codificano con 3 FF di tipo JK. La tabella degli stati futuri è la seguente:

| Stato          | $Q_2(t)$ | $Q_1(t)$ | $Q_0(t)$ | X | $\mathbf{J}_2$ | $\mathbf{K}_2$ | $\mathbf{J}_1$ | K <sub>1</sub> | $\mathbf{J_0}$ | $\mathbf{K}_{0}$ | $Q_2(t+1)$ | $Q_1(t+1)$ | $Q_0(t+1)$ | Z |

|----------------|----------|----------|----------|---|----------------|----------------|----------------|----------------|----------------|------------------|------------|------------|------------|---|

| C              | 0        | 0        | 0        | 0 | 0              | X              | 0              | X              | 1              | X                | 0          | 0          | 1          | 0 |

| $S_0$          | 0        | 0        | 0        | 1 | 0              | X              | 1              | X              | 0              | X                | 0          | 1          | 0          | 0 |

| $S_1$          | 0        | 0        | 1        | 0 | 1              | X              | 0              | X              | X              | 1                | 1          | 0          | 0          | 0 |

| $\mathbf{s}_1$ | 0        | 0        | 1        | 1 | 0              | X              | 1              | X              | X              | 1                | 0          | 1          | 0          | 0 |

| $S_2$          | 0        | 1        | 0        | 0 | 0              | X              | X              | 0              | 1              | X                | 0          | 1          | 1          | 0 |

| $\mathbf{S}_2$ | 0        | 1        | 0        | 1 | 0              | X              | X              | 0              | 0              | X                | 0          | 1          | 0          | 0 |

| $S_3$          | 0        | 1        | 1        | 0 | 1              | X              | X              | 1              | X              | 1                | 1          | 0          | 0          | 0 |

| $\mathbf{b}_3$ | 0        | 1        | 1        | 1 | 0              | X              | X              | 0              | X              | 1                | 0          | 1          | 0          | 1 |

| $S_4$          | 1        | 0        | 0        | 0 | X              | 0              | 0              | X              | 0              | X                | 1          | 0          | 0          | 1 |

| $\mathbf{S}_4$ | 1        | 0        | 0        | 1 | X              | 1              | 1              | X              | 0              | X                | 0          | 1          | 0          | 1 |

|                | 1        | 0        | 1        | 0 | X              | X              | X              | X              | X              | X                | X          | X          | X          | X |

|                | 1        | 0        | 1        | 1 | X              | X              | X              | X              | X              | X                | X          | X          | X          | X |

|                | 1        | 1        | 0        | 0 | X              | X              | X              | X              | X              | X                | X          | X          | X          | X |

|                | 1        | 1        | 0        | 1 | X              | X              | X              | X              | X              | X                | X          | X          | X          | X |

|                | 1        | 1        | 1        | 0 | X              | X              | X              | X              | X              | X                | X          | X          | X          | X |

|                | 1        | 1        | 1        | 1 | X              | X              | X              | X              | X              | X                | X          | X          | X          | X |

Applicando le mappe di Karnaugh si ottiene:

$$J_1 = x \; , \; K_1 = J_2 = Q_0 \cdot \overline{x} \; , \; K_2 = x \; , \; J_0 = \overline{Q_2} \overline{x} \; , \; K_0 = 1 \; , \; z = Q_2 + Q_1 \cdot Q_0 \cdot x$$

### Esercizio 3

Per ottenere il valore decimale di un numero in complemento a due  $c_{n-1}c_{n-2}...c_1$   $c_0$  si usa la seguente formula:

$$N = -c_{n-1}2^{n-1} + \sum_{i=0}^{n-2} c_i 2^i$$

per n = 3 e al variare della sequenza di bit si ottiene:

| Compl. a 2 | Decimale |

|------------|----------|

| 000        | 0        |

| 001        | 1        |

| 010        | 2        |

| 011        | 3        |

| 100        | -4       |

| 101        | -3       |

| 110        | -2       |

| 111        | -1       |

# Soluzione compito D

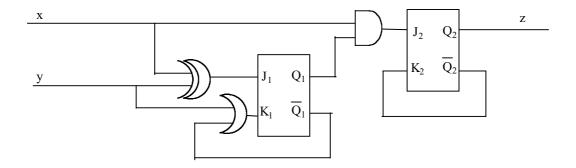

## Esercizio 1

Si ha:

$$J_1 = x \oplus y$$

$$K_1 = y + \overline{Q_1}$$

$$J_2 = x \cdot Q_1$$

$$K_2 = \overline{Q_2}$$

$$z = Q_2$$

Il diagramma degli stati è il seguente:

| X | y | $Q_2(t)$ | $Q_1(t)$ | $J_2$ | $\mathbf{K}_2$ | $\mathbf{J}_1$ | $\mathbf{K}_{1}$ | $Q_2(t+1)$ | $Q_1(t+1)$ | Z |

|---|---|----------|----------|-------|----------------|----------------|------------------|------------|------------|---|

| 0 | 0 | 0        | 0        | 0     | 1              | 0              | 1                | 0          | 0          | 0 |

| 0 | 0 | 0        | 1        | 0     | 1              | 0              | 0                | 0          | 1          | 0 |

| 0 | 0 | 1        | 0        | 0     | 0              | 0              | 1                | 1          | 0          | 1 |

| 0 | 0 | 1        | 1        | 0     | 0              | 0              | 0                | 1          | 1          | 1 |

| 0 | 1 | 0        | 0        | 0     | 1              | 1              | 1                | 0          | 1          | 0 |

| 0 | 1 | 0        | 1        | 0     | 1              | 1              | 1                | 0          | 0          | 0 |

| 0 | 1 | 1        | 0        | 0     | 0              | 1              | 1                | 1          | 1          | 1 |

| 0 | 1 | 1        | 1        | 0     | 0              | 1              | 1                | 1          | 0          | 1 |

| 1 | 0 | 0        | 0        | 0     | 1              | 1              | 1                | 0          | 1          | 0 |

| 1 | 0 | 0        | 1        | 1     | 1              | 1              | 0                | 1          | 1          | 0 |

| 1 | 0 | 1        | 0        | 0     | 0              | 1              | 1                | 1          | 1          | 1 |

| 1 | 0 | 1        | 1        | 1     | 0              | 1              | 0                | 1          | 1          | 1 |

| 1 | 1 | 0        | 0        | 0     | 1              | 0              | 1                | 0          | 0          | 0 |

| 1 | 1 | 0        | 1        | 1     | 1              | 0              | 1                | 1          | 0          | 0 |

| 1 | 1 | 1        | 0        | 0     | 0              | 0              | 1                | 1          | 0          | 1 |

| 1 | 1 | 1        | 1        | 1     | 0              | 0              | 1                | 1          | 0          | 1 |

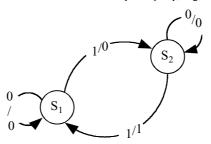

## Esercizio 2

L'automa minimizzato è costituito da due soli stati  $S_1$ ' = {  $S_1$ ,  $S_2$ ,  $S_3$ ,  $S_6$  } e  $S_2$ ' = {  $S_4$ ,  $S_5$ ,  $S_7$ ,  $S_8$  }:

La codifica con 1 FF di tipo JK è immediata:

| X | $Q_1(t)$ | $\mathbf{J}_1$ | $\mathbf{K}_{1}$ | $Q_1(t+1)$ | Z |

|---|----------|----------------|------------------|------------|---|

| 0 | 0        | 0              | X                | 0          | 0 |

| 0 | 1 | X | 0 | 1 | 0 |

|---|---|---|---|---|---|

| 1 | 0 | 1 | X | 1 | 0 |

| 1 | 1 | X | 1 | 0 | 1 |

Applicando Karnaugh si ottiene:

$$J_1 = x , K_1 = x$$

infine banalmente  $z = x \cdot Q_1$

### Esercizio 3

Per ottenere il valore decimale di un numero in complemento a due  $c_{n-1}c_{n-2}...c_1$   $c_0$  si usa la seguente formula:

$$N = -c_{n-1}2^{n-1} + \sum_{i=0}^{n-2} c_i 2^i$$

per cui si ha:

$$0011 = 2^{1} + 2^{0} = 2 + 1 = 3$$

$$1111 = -2^{3} + 2^{2} + 2^{1} + 2^{0} = -8 + 4 + 2 + 1 = -1$$